什么是建立时间和保持时间, 为什么需要考虑它们?

D触发器

亚稳态问题

(复位中也需要)

时钟从哪里来?

FPGA结构 参考

时钟树

Local Clocks

In general, avoid using local clocks建议来源

如何确认是否使用了local clocks: 通过report_clock_utilization命令

PLL和MCMM

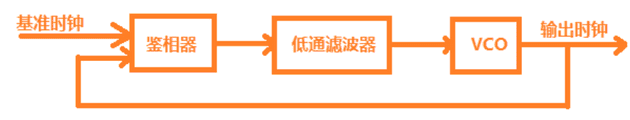

PLL(Phase Locked Loop),生成时钟的核心部分是 压控振荡器 (Voltage-Controlled Oscillator,VCO)。它是可根据 输入的电压调整输出频率 的振荡器,如上图所示。

它的基本原理是通过 负反馈 形成闭环从而根据输入的基准时钟控制输出时钟。其中鉴相器就相当于一个 比较器 ,它根据基准时钟和输出时钟的差值转换为控制电压,输出到低通滤波器滤除高频杂波,然后输入到VCO,VCO主频过高则降低电压,反之提升电压,使输出时钟跟随给定的基准时钟。

PLL(Phase Locked Loop),生成时钟的核心部分是 压控振荡器 (Voltage-Controlled Oscillator,VCO)。它是可根据 输入的电压调整输出频率 的振荡器,如上图所示。

它的基本原理是通过 负反馈 形成闭环从而根据输入的基准时钟控制输出时钟。其中鉴相器就相当于一个 比较器 ,它根据基准时钟和输出时钟的差值转换为控制电压,输出到低通滤波器滤除高频杂波,然后输入到VCO,VCO主频过高则降低电压,反之提升电压,使输出时钟跟随给定的基准时钟。

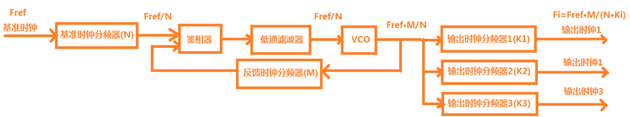

基准时钟经过分频器后输出频率为 Fref/N ,并输入到鉴相器 。 为了要让鉴相器与反馈频率相同,VCO的输出频率Fvco需要让反馈频率在经过反馈时钟分频器后输出到鉴相器的频率和分频后的基准时钟频率相同,所以 Fvco=M/N·Fref 。 Fvco经过输出时钟分频器输出的时钟为 Fi=Fref·M/(N·Ki) ,其中Fi为输出频率,Fref为基准时钟的频率,Ki为输出时钟分频比,N为基准时钟分频比,M为反馈时钟分频比。

MMCM是一种带有附加逻辑的 PLL,用于进行精细相位调整。因此,MMCM 的相位略优于 PLL,但本质上它们都是 PLL。(The MMCM is a PLL with additional logic to do fine phase adjustments. So, the MMCM has slight phase advantages over the PLL, but at the heart they are both PLLs.MMCM )参考与更详细的解释