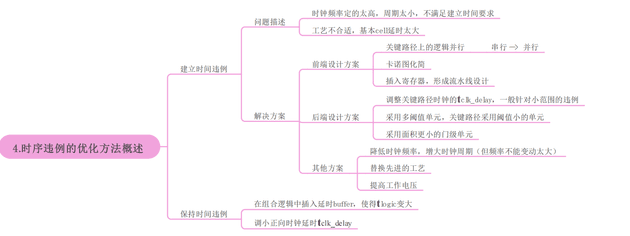

时序分析工具

report_design_analysis/report timing summary查看时序分析报告,分析logic level, logic delay, net delay(route delay), fanout等信息。Clock Skew,当其绝对值超过 500ps 时,应引起关注。Clock Uncertainty,当该数值超过 100ps 时,应引起关注。来源

通过report_qor_suggestions生成结果质量 (QoR) 评估报告 (Report Quality of Results (QoR) Assessment)将逻辑层次检查、利用率检查和最常用的时钟拓扑结构检查组合到单一汇总报告中,以便为您提供总体设计评估。此报告可帮助您了解时序收敛问题的严重性。来源

什么造成了时序分析失败?

fanout过大

导致:

- 布线拥塞

- 驱动能力变弱(下级电路的输入电容增大, transition所需时间增大)

诊断方法

查看timing summary

解决办法

- 寄存器复制

- verilog/xdc中设置max_fanout属性

- 设置MAX_FANOUT

- BUFG增加时钟扇出

net delay过高

由route过长造成

诊断方法

对于违例路径,若布线延迟超过 50%,说明该延迟是导致时序不能收敛的主要因素,因此可围绕降低布线延迟这一靶心达到时序收敛。

解决办法

set_input_delay/set_output_delay/set_max_delay

- set_input_delay: 指定输入数据引脚相对于其时钟沿的路径延时

- set_output_delay: 指定输出数据引脚相对于其时钟沿的路径延时

- set_max_delay: 设置数据路径的最大延迟(-from -to)

参数:

- max: 定义了输入信号到达端口的最迟时间,用于建立时间分析

- min: 定义了输入信号到达端口的最快时间,用于保持时间分析。(延时太小,FPGA端的保持时间可能不满足)

调FPGA内部时序的时候,端口的时序可以先放一下,比如set_input_delay, set_put_delay 约束可以先不加,再看一下整个设计的跑的情况,看下有问题的路径,确定如何来优化时序.来源

set_input_delay/set_output_delay

logic delay过高

由于logic level过高导致data path过长,造成logic delay过高,时序分析失败

诊断方法

Logic Level Distribution分析延时原因详解

一个经验法则是,LUT(查找表)加上NET(网络)的延迟大约是0.5ns。如果时钟周期为5ns,则电路中最大的级联数应该是5ns / 0.5ns = 10级 来源

解决办法

流水线化

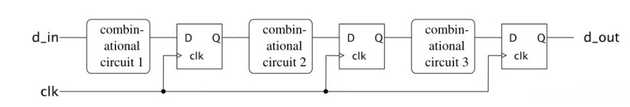

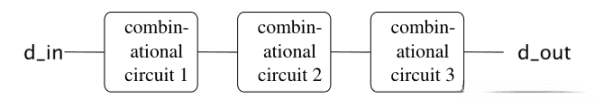

这是原本只有组合逻辑电路的设计,组合逻辑总延迟为total_delay = delay1 + delay2 + delay3

这是原本只有组合逻辑电路的设计,组合逻辑总延迟为total_delay = delay1 + delay2 + delay3

并且我们要求total_delay < clock_period

这是流水线化后的设计,中间添加了寄存器,由此组合逻辑被分成了三个阶段,每个阶段的延迟为delay1, delay2, delay3

我们只需要max{delay1, delay2, delay3} < clock_period即可

虽然信号传递时长增加了,但是每个输出数据之间间隔依旧是只有一个时钟周期,并且允许更高的时钟频率

建议数据输出到管脚前用寄存器打一拍,这样IO上的时序比较容易满足。这条路径如果在输出前用寄存器打一拍时序就很容易满足了

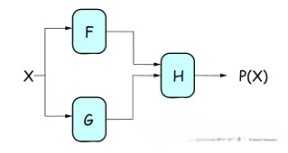

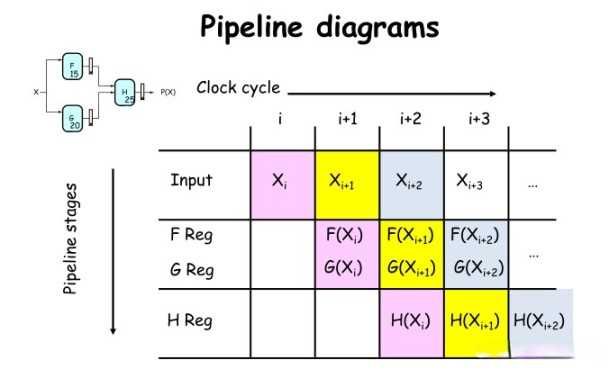

上图为二阶流水线

- K阶流水线(“k-pipeline”)是一种无循环电路,其在从输入到输出的每个路径上具有恰好k个寄存器。因此,组合电路是0阶流水线。

- k阶流水线的延迟是所有寄存器通用时钟的k倍。

- k阶流水线的吞吐量是时钟的频率。

手动retiming优化

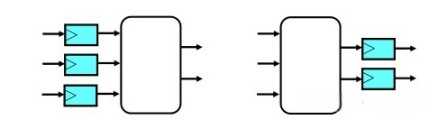

上图将一组寄存器从组合逻辑的左边移动到另一边,改善了右边时序的压力,但也会增加左边逻辑的压力

上图将一组寄存器从组合逻辑的左边移动到另一边,改善了右边时序的压力,但也会增加左边逻辑的压力

如果一方的压力较大,一方的压力较小,就可以通过这种切割关键路径的方式改善关键路径时序(关键时序路径就是延迟最大的路径)。

自动retiming优化

-

RETIMING_FORWARD: 寄存器沿着逻辑链向前移动,即向驱动顺序元件的方向移动(register forward through logic closer to the driven sequential elements)RETIMING_FORWARD官方文档

-

RETIMING_BACKWARD: 寄存器沿着逻辑链向后移动,即向顺序驱动元件的方向移动(register backward through logic closer to the sequential driving elements)RETIMING_BACKWARD官方文档