经验

Vivado使用经验

doesn't exist问题/自定义ip核not found问题(HLS ip核尤其可能发生)/任何block design的奇怪问题

- 先尝试重新打开vivado,如果没解决,进行下一步

- 在block design中删除对应ip,保存,然后重新添加(ctrl+z或者重新加入重新连)

vivado版本不同ip核升级问题

a. 不升级ip核,以只读方式查看

b. 安装对应版本vivado

vivado block design interface连线问题

一旦interface中的任何signal被从interface中展开, 那么对于这个interface的interface级别的连线都不会包含这个signal

Vitis HLS使用经验

提升代码编写效率

不管是Vitis HLS还是Xilinx Vitis,它们的代码提示功能都不是很好,所以可以使用vscode进行代码编写,将相应头文件编辑入 vscode插件的include path中, 可以获得更好的代码提示

并且,copilot插件可以帮助我们生成代码及获得建议

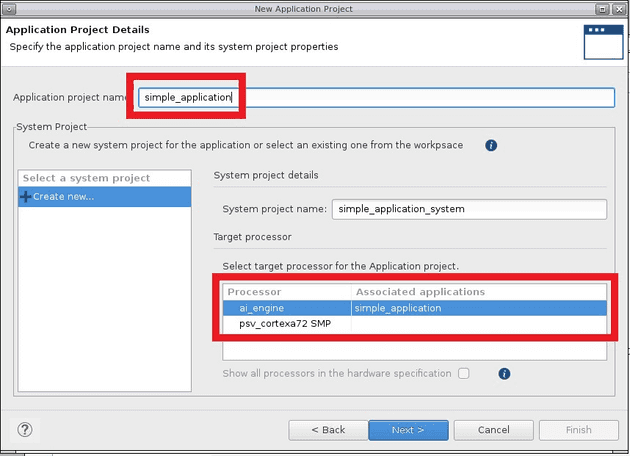

Vitis使用经验

update hardware specification后program FPGA时依旧是旧硬件问题

vitis的run configuration取消勾选reset entire system和program FPGA选项, 通过vivado端program FPGA,然后再在Vitis端进行PS代码的烧录

但是,如果PL端的ip核更新,一定要在vivado端重新生成bitstream,然后在vitis端重新update hardware specification

预测

目前方式(verilog/HLS)的PL端神经网络加速不会成为主流

目前的PL端神经网络加速的问题,一言以蔽之,就是生态不好,设计和验证成本太高,目前的PL端加速在我看来没有太大的搞头, 在未来这种设计方式必然被一种更具通用性的设计方式取代,如现在rknn-toolkit的方式,神经网络进行转化或者读取之后直接地进行部署 ,并提供sdk,使得对神经网络新发或者小众的层可以由用户写下相应算子供toolkit转换

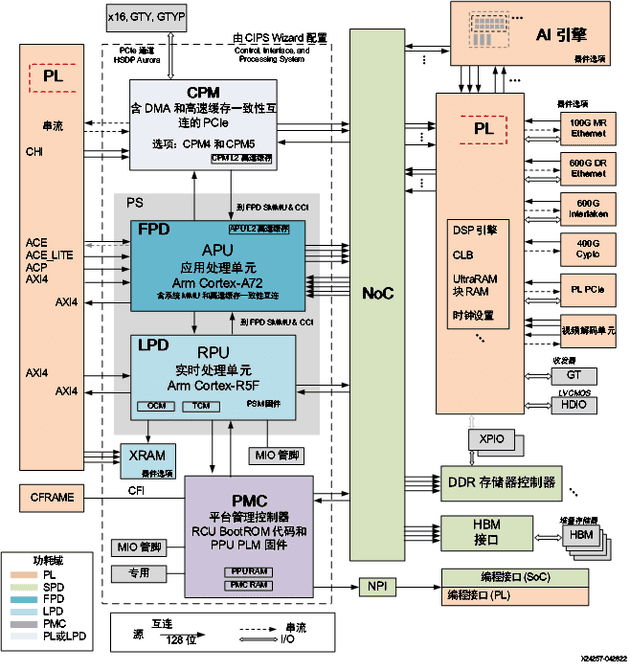

同时,Versal的推出,意味着主流的趋势是PL端专门一个特化的AI处理器,然后对其进行软件开发(目前为C语言), 这样的设计方式更具通用性,容易维护、开发

下图为Versal的架构图

FPGA部分为什么重要

如果说现实也有一个帧率"现实帧率",那么FPGA的重要性就体现在FPGA可以提供更高的帧率,以图逼近现实帧率, 更快地处理速度使FPGA在控制系统中具有十分重要的地位,这种价值在工业商业应用上体现在它的实时性上, 换言之,只要工业商业对于实时性的要求不减,那么FPGA的地位就不会被取代

异核处理器将成为主流

FPGA的高速处理能力和ARM的通用处理能力结合,甚至更高端嵌入式的fpga+npu的结合,将成为主流. 从Versal的架构中包含了PL,PS和ai引擎这一特征中,也可以看出这种结合的趋势

商业前景:

- 车机系统,车机系统的要求是出于安全考虑要求实时性高,处理速度快,而且需要神经网络来进行识别和避障

- 工业控制系统,工业控制系统对于实时性的要求也是很高的,而且需要神经网络来进行识别和控制

- 搭载自动驾驶的无人机,理由同上